Xilinx 고속 신호선의 Ref Clock이 두개인 이유

1. 고속 Transceiver

Xilinx FPGA 를 사용하다보면 FPGA의 IO핀의 입출력 최대 클럭 속도보다 빠른 속도가 필요한 경우가 있다. (시리즈마다 다르지만 IO는 1.2Gb/s 정도) 예를들면 LVDS, V-by-one, HDMI 등인데 이를 위해 전용으로 나온 IO가 고속 Transceiver 이다.

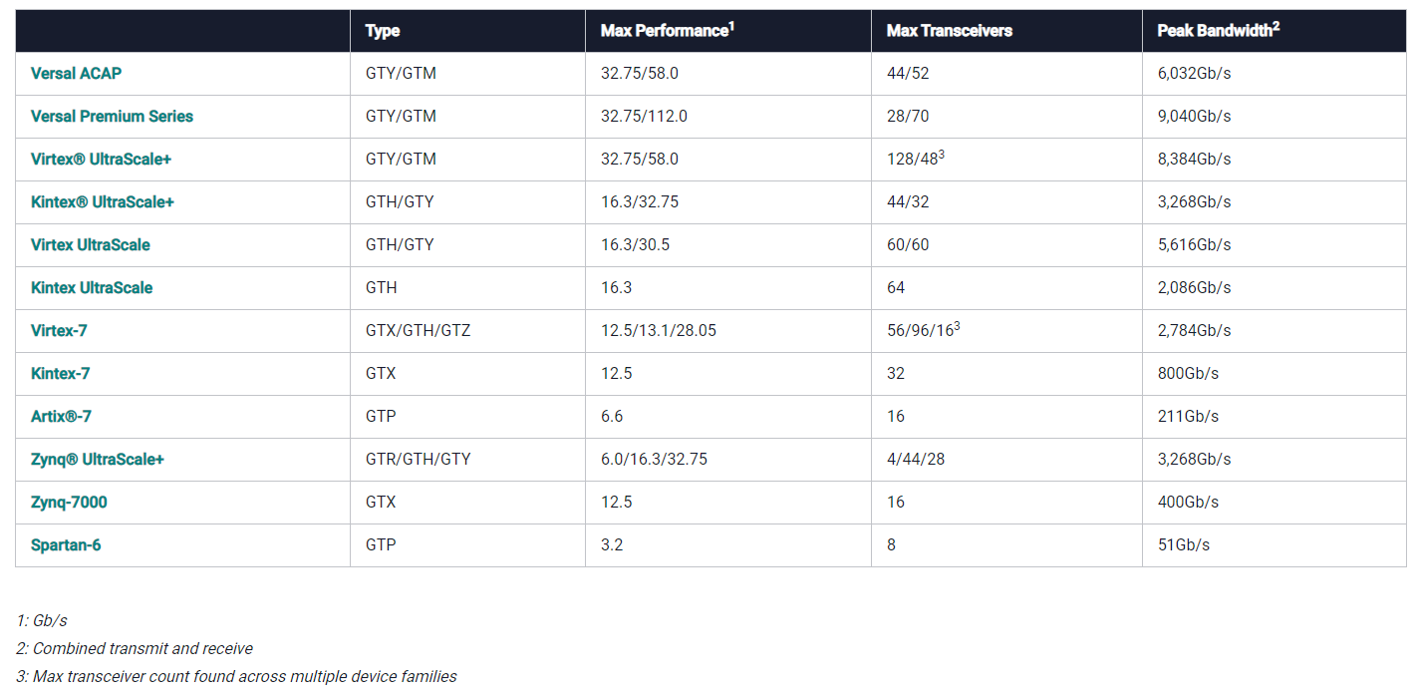

Xilinx는 지원하는 속도에 따라서 이름을 분리했는데 GTP/GTR/GTX/GTH/GTZ/GTY/GTM (후…많다…) 정도 되겠다.(아래표 참조)

2. 고속 Transceiver의 Ref Clock

보통 고속 Transceiver는 Quad로 묶여 있는데 Common Ref Clock(X0Y0)에 4개의 Channel(X0Y0~X0Y3)로 묶여 있다.(하나의 채널은 P, N Differential Pair) 이름은 번호로 할당되어 있지만 내부 로직에서 핀 Assign을 어떻게 하느냐에 따라 원하는데로 선택적 사용을 할 수 있다. 그런데 Common Ref Clock이 두개의 입력을 받을 수 있게 되어 있어 이유를 확인하다보니 포스팅을 하게 되었다.

3. 결론

결론부터 얘기하면 설계 유동성 때문에 Common Ref Clock이 두개가 있는 것이다. 만약 PCIe 2레인과 LVDS 2레인을 사용하고 싶은데 Ref Clock이 서로 다르고 Common Ref Clock이 한개 밖에 없다면 4개의 채널을 다 사용하지 않지만 PCIe와 LVDS 중 하나를 선택 할 수 밖에 없다. 하지만! Xilinx FPGA 설계자들은 이를 미리 알고 고속 Transceiver를 최대한 활용할 수 있도록 최대 2개까지의 외부 클럭을 받을 수 있게 만들어둔 것이다. 보통 고속 Transceiver가 지원되는 개수에 따라 FPGA 가격이 상승하게 되는데 효율적인 설계와 확장성을 고려한 부분이라고 할 수 있겠다.

도움이 되셨다면 더 좋은 정보 공유를 위해 광고 클릭 부탁 드립니다 :)

![[codex] Ubuntu에서 Codex CLI 설치하기 (Node 버전 오류 + 권한 문제 해결)](https://1.bp.blogspot.com/-pK1xNaTx36M/YJMrtBs5gsI/AAAAAAAACGI/M2gettChjN0lJufd9M9yoctbddtopRvuACLcBGAsYHQ/w72-h72-p-k-no-nu/laptop-5906264_640.png)

![[python] Python Arduino and serial communication](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEi3C4-Ii1rGAh2KJ0psBHhxgQwjFxgA4RBerMSN3Q2o2GewXpXpyxxTgXZ4PDFVR-wIcmdmINuf_N7QNeNRCfHKCPT1mwFbn2yhex2fiDeNSl6T8kgWkTG71VkFqIXsIgBZFrIHxBRusqI0/w72-h72-p-k-no-nu/laptop-5906264_640.png)

0 댓글